A compendium of blog posts on op amp design topics

by Bruce Trump

## CONTENTS

### Preface

### I. Op Amp Voltage: Range Issues

- 1. Op amp voltage ranges: input and output, clearing some confusion

- 2. Rail-to-rail inputs: what you should know

- 3. Swinging close to ground: single-supply operation

### II. Offset Voltage

- 4. Offset voltage and open-loop gain: they're cousins

- 5. SPICEing offset voltage: how to check the sensitivity of circuits to offset voltage

- 6. Where are the trim pins? Some background on offset-voltage trim pins

### **III. Input Bias Current**

- 7. "I need high input impedance!" Input impedance vs. input bias current

- 8. Input bias current of CMOS and JFET amplifiers

- 9. Temperature effects on input bias current, plus a random quiz

- 10. Input bias current cancellation resistors: do you really need them?

- 11. Internal input bias current cancellation of bipolar op amps

#### **IV. Stability and Oscillations**

- 12. Why op amps oscillate: an intuitive look at two frequent causes

- 13. Taming the oscillating op amp

- 14. Taming oscillations: the capacitive load problem

- 15. SPICEing op amp stability

- 16. Input capacitance: common mode? Differential? Huh?

- 17. Op amps: G = 1 stable and decompensated

- 18. The inverting attenuator G = -0.1: is it unstable?

### **V. Dynamic Behavior**

- 19. Simulating gain bandwidth: the generic op amp model

- 20. Slew rate: the op amp speed limit

- 21. Settling time: a look at the character of the settling waveform

### VI. Noise

- 22. Resistor noise: reviewing basics, plus a fun quiz

- 23. Op amp noise: the noninverting amplifier

- 24. Op amp noise: but what about the feedback resistors?

- 25. 1/f noise: the flickering candle

- 26. Chopper op amps: are they really noisy?

#### VII. Other Op Amp Issues

- 27. Bypass capacitors: yes, they are needed, but why?

- 28. The unused op amp: what to do?

- 29. Protecting inputs from EOS over-voltage

- 30. Differential input clamps: can they affect your op amp circuits?

- 31. Op amps used as comparators: is it okay?

#### VIII. More Content

32. More content and links

## Preface

Learning analog seems like a daunting task. Analog engineers do not generally acquire their experience in a linear path from start to finish: They zigzag a path through an obstacle course of hurdles. They acquire insights in small pieces – a bit here and a bite (not a byte) there. Slowly, puzzle pieces fit into place, and hazy concepts come into focus.

We will never have the satisfaction of jumping a final hurdle or tapping the final puzzle piece into place; that just won't happen. Colleagues much smarter than I am cannot answer all of my questions ... and I cannot answer all of yours.

So this assemblage of little analog lessons is hopelessly incomplete. Still, I think you will find it helpful. It may fill some gaps in your knowledge or stimulate your thinking. Each topic addressed in this book was originally published as a post on my blog, "<u>The Signal</u>," which you can still visit on <u>TI's E2E</u><sup>TM</sup> <u>Community</u>. As such, you'll find that the lessons are short and to the point; practical and intuitive; bite-sized and easy to digest. I needed it to be that way because I'm a simple guy with little patience.

Most of my blog posts sparked questions and other dialogue. I have included links at the end of each topic to the original post when comments were posted. I think you will find some valuable lessons taught there. Furthermore, this compendium does not include all of my blogs. I've included links to other topics, at the end.

If you have any questions about the topics I cover here, or any other precision-amplifier questions for that matter, I hope you will submit them to the Precision Amplifiers forum on TI's E2E Community.

For reference, I created most of the images in this e-book using TI's <u>TINA-TI</u><sup>™</sup> free software tool, downloadable from TI's website.

### About the Author

## **Bruce Trump**

As a boy experimenter and ham radio operator, Bruce Trump was drawn to electrical engineering. He never doubted that this was his career path.

After earning a bachelor's degree from Iowa State University, his first industry job took him to Ohio, where he worked on an early laser memory system and other analog system components.

His next stop was at Heath Co. in Michigan designing Heathkits. He tackled a variety of projects there, including electronic clocks, megaphones, metal detectors, navigation calculators and high-power stereo amplifiers.

But hard-core analog was calling him. Burr-Brown, which was a leading provider of analog integrated circuits at that time, offered Bruce an opportunity in Tucson, Arizona, to hang out with and learn from real analog experts.

Texas Instruments acquired Burr-Brown in 2000, marking a new chapter in Bruce's analog career, which included roles in product development, product definition, applications engineering, technical literature, product promotion and business management.

When Bruce reflects on his career, he typically shares that his favorite activity was always dealing with customer application issues.

"I always seemed to work this into whatever role I was currently playing. I particularly enjoyed developing customer seminars and datasheets. It was a challenge to clearly explain the inner workings and applications of precision analog components," he said.

# 1. Op amp voltage ranges: input and output, clearing some confusion

System designers often have questions about the power supply input and output voltage-range capabilities of <u>operational amplifiers</u> (op amps). It can be confusing, so here is my attempt to sort it out.

First, common op amps do not have ground terminals. A standard op amp does not "know" where ground is, so it cannot know whether it is operating from a dual supply (±) or a single power supply. As long as the power-supply input and output voltages are within their operating ranges, all is well.

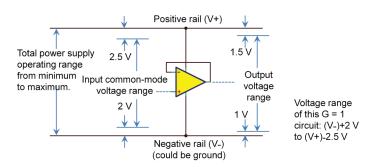

Here are three critical voltage ranges to consider:

- The total supply-voltage range. This is the total voltage between the two supply terminals. For example, ±15 V is a total of 30 V. The operating voltage range for an op amp might be 6 V to 36 V, for example. At the low-voltage extreme, this could be ±3 V or +6 V. At maximum, it could be ±18 V or +36 V or even -6 V/+30 V. Yes, unbalanced supplies are OK, but only if you heed the second and third bullet points below.

- The input common-mode voltage range (C-M range) is generally specified relative to the positive and negative supply voltages, shown in Figure 1. In some equation-like form, the C-M range of this hypothetical op amp would be described as 2 V above the negative rail to 2.5 V below the positive rail. Something like this: (V-)+2 V to (V+)-2.5 V.

- 3. The output-voltage range (or output-swing capability) is, again, commonly specified relative to the rail voltages. In this case, (V–)+1 V to (V+)–1.5 V.

Figures 1, 2 and 3 show a G = 1 buffer configuration. A key point here: The output capability of the example in Figure 1 will be limited to 2 V from the negative rail and 2.5 V from the positive rail, which is due to the limited-input C-M range. You would need to configure this op amp in a higher gain to deliver its full output-voltage range.

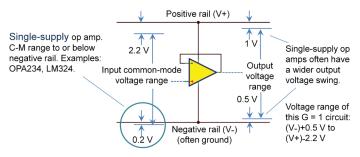

**Figure 2** shows a so-called single-supply op amp. It has a C-M range that extends to, and often slightly below, the negative rail. That range allows its use in a wider range of circuits that operate close to ground. So an op amp that is not called "single supply" is actually usable in some single-supply circuits, but a true single-supply type is more versatile.

Figure 2: Input and output voltage ranges of a typical single-supply op amp.

In a G = 1 buffer circuit, this op amp could produce an output swing of 0.5 V from the V– rail (limited by the output capability) and 2.2 V from the V+ rail (limited by the input C-M range).

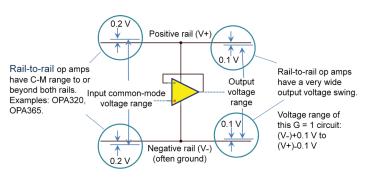

**Figure 3** shows a "rail-to-rail" op amp. It can operate with an input voltage equal to or even slightly beyond both supply-voltage rails, as shown in **Figure 3**. A rail-to-rail output means that the output voltage can swing very close to the rails, often within a 10- to 100-mV range from the supply rails. Some op amps claim only a rail-to-rail output, lacking the input characteristics shown in **Figure 3**. Rail-to-rail op amps are very commonly used on single 5-V supplies and lower because they maximize the signal-voltage capability on their limited supply range.

#### Figure 3: Input and output voltage ranges of a typical rail-to-rail op amp.

Rail-to-rail op amps are appealing because they ease signal-voltage constraints, but they are not always the best choice. Like other life choices, there are often trade-offs with other performance attributes. But that is why you are an analog designer. Your life is full of complex issues and trade-offs, and you love it!

To see this original post with comments, click here.

# Figure 1: Input and output voltage ranges of a typical op amp used on dual supplies (±).

The example in **Figure 1** is typical of an op amp generally used on dual supplies. It would not be called a "single-supply" type, but it could operate as a single supply by staying within those ranges.

## 2. Rail-to-rail inputs: what you should know!

Rail-to-rail <u>operational amplifiers</u> (op amps) are extremely popular and especially useful with low supply voltages. You should know how to accomplish rail-to-rail inputs and understand some trade-offs.

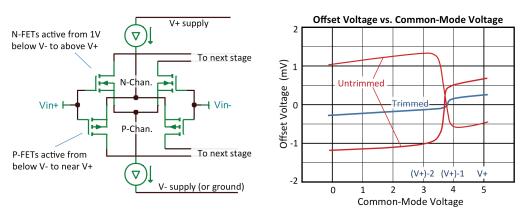

**Figure 4** shows a typical dual-input, rail-to-rail stage comprising both N-channel and P-channel transistor pairs. P-channel field-effect transistors (FETs) handle the signal through the lower portion of the <u>common-mode voltage range</u> to slightly below the negative rail (or single-supply ground). The N-channel FETs operate with a common-mode voltage near and slightly above the positive rail. Additional circuitry (not shown) directs traffic, determining which input-stage signal the next stage will process. Most TI dual-input-stage op amps are designed so that the transition occurs approximately 1.3 V from the positive rail. Above this voltage, there is insufficient gate voltage for the P-channel stage, so the signal path is redirected to the N-channel stage.

Figure 4: A typical dual-input rail-to-rail stage using both N- and P-channel transistor pairs.

The P and N input stages will have somewhat different offset voltages. If the common-mode voltage moves through this transition (as it does with rail-to-rail G = 1 operation), it creates a change in the offset. Some op amps are factory-trimmed by laser or electronic trimming, adjusted to reduce the offset of the input stages. This trimming reduces the change through the transition but still leaves a residual bobble. Circuitry controlling the transition from the P to N input stage is referenced to the positive supply voltage, not to ground. On a 3.3-V supply, the transition moves to an awkward point – midsupply.

While unnoticed in most applications, this change in offset voltage may be an issue if you require high accuracy. It can also cause distortion in alternating current (AC) applications. But again, distortion will only occur if the common-mode input voltage crosses the transition between stages.

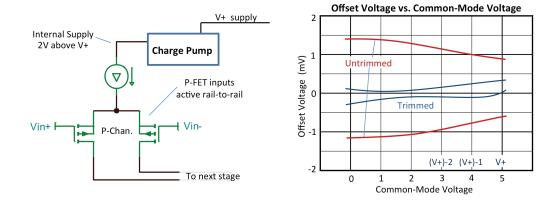

**Figure 5** shows a second type of rail-to-rail input stage. An internal charge pump boosts the voltage powering a single P-channel input stage to approximately 2 V above the positive supply rail. This voltage boost allows a single-input stage to perform seamlessly over the full rail-to-rail input-voltage range – below the bottom rail to above the top rail – with no transition glitch.

Figure 5: A rail-to-rail input stage with an internal charge pump to boost the voltage, powering a single P-channel FET.

"Charge pump" ... it sounds spooky to some designers. They are noisy, right? But TI's most recent ones are remarkably quiet. Charge pumps require very little current because they only power the input stage. There are no extra pins or capacitors – it is all internal. Chargepump noise is below the broadband noise level; rarely can you see it in the time domain. Applications that analyze the spectral response below the broadband noise level, however, may see some artifacts.

Not all applications need an op amp with rail-to-rail input. Inverting op amp circuits or amplifiers in gain greater than unity, for example, often do not require rail-to-rail input, yet still have rail-to-rail output. Do you really need a rail-to-rail input amplifier? Many engineers prefer to use them so that they do not need to worry about exceeding the common-mode range. They use the same op amp in various points in their systems: some need rail-to-rail input; others not. Whatever your choice, with knowledge of rail-to-rail types and trade-offs, you can select more wisely. If in doubt, you are welcome to ask the engineers on the TI E2E<sup>™</sup> Community <u>Precision Amplifiers forum</u>.

Here are a few example op amps:

- <u>OPA340</u> dual-input stage, trimmed offset, 5.5-MHz, rail-to-rail CMOS.

- <u>OPA343</u> dual-input stage, untrimmed offset, 5.5-MHz, rail-to-rail CMOS.

- <u>OPA320</u> charge-pumped input stage, 20 MHz, rail-to-rail CMOS.

- <u>OPA322</u> charge-pumped input stage, untrimmed offset, 20 MHz, rail-to-rail CMOS.

To see this original post with comments, <u>click here</u>.

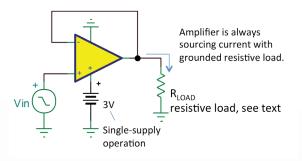

# 3. Swinging close to ground: single-supply operation

Rail-to-rail amplifiers can produce output voltages very close to ground – but how close? I am talking about complementary metaloxide semiconductor (CMOS) <u>operational amplifiers</u> (op amps) that often are used in low-voltage designs when you are trying to maximize output-voltage swing. TI's specifications for these devices generally look something like Table 1.

| Parameter                 | Conditions          | Min | Тур | Max | Unit |

|---------------------------|---------------------|-----|-----|-----|------|

| Output                    |                     |     |     |     |      |

| Voltage output swing from | $RL = 10 \ k\Omega$ |     | 15  | 25  | mV   |

| both rails                | $RL = 2 k\Omega$    |     | 35  | 50  | mV   |

Table 1: Output specifications for rail-to-rail amplifiers.

Table 1 makes it appear that the output will never swing much closer than 15 mV from ground, and that last 15 mV can be critical for accurate zero-based measurements. But wait: You really need to carefully interpret all of the conditions of this specification, because the assumption is that the load is connected halfway between the power-supply terminals.

You will often find conditions cited at the top of the specifications table, where you will see a statement like this:  $R_1$  connected to  $V_s/2$ .

In this specified condition, the amplifier must sink current through the load resistor as the output approaches ground. This reflects the way the amplifier is tested, assuring that it can properly source and sink current. It is a sensible and conservative way to test and specify the amplifier, but what if it is not the way your load is connected? Suppose your load is connected to ground as in **Figure 6**. The load resistor actually helps pull the output to ground, and the amplifier is not required to sink current.

In this condition, most CMOS op amps can swing very close to ground – within a millivolt or two. The specifications may not highlight this capability, but it is hinted at in **Figure 7**, showing output-voltage swing as a function of output current. The graph could perhaps benefit from more resolution, but you can see that the output voltage converging on the specified voltage rails for this test is  $\pm 2.75$  V. For single-supply operation, the V– supply is equal to 0 V.

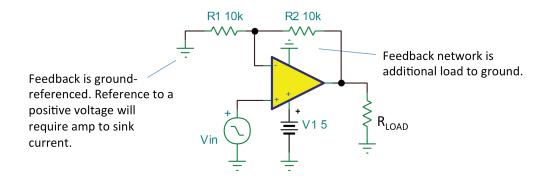

Now I need to add a few provisions. Notice that in **Figure 8**, the feedback network is referenced to ground. You need to consider all sources of load on the amplifier, not just RL. In this case, R1 + R2 are effectively additional ground-referenced loads in parallel to RL. But if R1 is referenced to a positive voltage, the amplifier would have to sink current coming through the feedback network as the output neared 0 V. The output would not be able to swing quite so close to ground.

In this same circuit, if the gain is high, the input offset voltage may affect your apparent output swing. For example, in G = 20, if the input offset voltage of the op amp is +1 mV, zero input will produce a 20-mV output. That is not due to an output-swing limitation – it is

an offset-voltage issue. Of course, a small, negative input voltage will bring the output very near 0 V, but your circuit may never have a negative input voltage.

Alternating current (AC) signals with reactive loads may be an exception. Load current and voltage are not in phase with a reactive load, so the amplifier may have to sink current as the output voltage approaches ground.

(Referring to CMOS op amps, bipolar op amps cannot swing so close to ground.)

Low-voltage battery-operated circuits are challenging, and it seems that we are always struggling to maximize voltage swings. With a good understanding of op amp capabilities, you may be able to squeak out additional output swing close to ground. If you have questions about a specific amplifier or circuit configuration, submit your question to the <u>Precision Amplifiers forum</u> on TI's E2E Community.

OUTPUT VOLTAGE SWING vs OUTPUT CURRENT (Over Temperature) 3 +2.75V 2 Output Voltage Swing (V) 1 +25°C 0 +125°C Output swings to -40°C supply voltages with -1 zero load current. -2 V<sub>S</sub> = ±2.75 V -2.75V -3 0 5 10 15 20 25 30 35 40 Output Current (mA)

Figure 8: Single-supply op amp configuration with the feedback network referenced to ground.

# 4. Offset voltage and open-loop gain: they are cousins

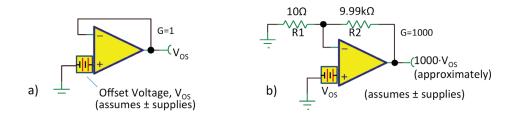

Everyone knows what offset voltage is, right? In the simplest G = 1 circuit of **Figure 9a**, the output voltage is the offset voltage of the <u>operational amplifier</u> (op amp). The offset voltage is modeled as a direct current (DC) voltage in series with one input terminal. In unity gain, the offset is passed directly to the output with G = 1. In the high-gain circuit (**Figure 9b**), the output voltage is 1000 Vos. Right?

Well, nearly so, but not quite. Understanding the "not quite" can help you understand errors in your op amp circuits.

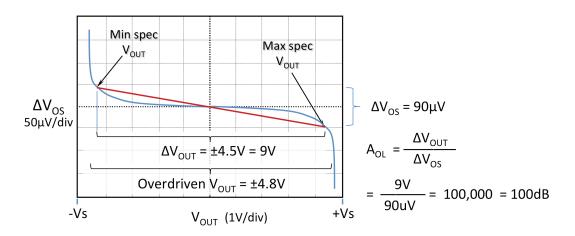

In the first case, the output voltage was very near midsupply (assuming dual supplies). This is the output voltage at which TI defines and tests offset voltage. But in the second case, the output may be several volts, assuming several millivolts of offset. That requires a small additional differential voltage at the input of the op amp to create the output swing (according to the open-loop gain of that particular amplifier). Let us run some numbers. "If the DC open-loop gain is 100 dB, that amounts to  $1/10^{(100 \text{ dB}/20)} = 10 \,\mu\text{V/V}$ . So for every volt of output swing from midsupply, the input voltage must change by 10  $\mu$ V. Think of it as an offset voltage that changes with the DC output voltage. With 9 V of output swing, that is a 90- $\mu$ V change. Maybe that is insignificant in your circuits, maybe not.

The point is that thinking of finite open-loop gain as a changing offset voltage with a change in output voltage provides an intuitive way to size up the error. And the character of that error may matter, too. To test offset voltage and open-loop gain, use a fancy two-amp loop circuit. With it, you can control the output voltage and measure the offset voltage. If you sweep the output voltage through its full output range, the change in offset voltage often looks something like Figure 10.

Note that the greatest change in offset voltage tends to occur at the output extremes, near the positive and negative rail. The op amp is "straining" to produce its maximum output. The incremental openloop gain is higher in the middle and falls where the output nears the rails. As you plan your circuits, expect that this will be the case. Offset voltage will increase more dramatically as you push the op amp to its swing limits.

Figure 9: Output offset voltage where G = 1 V/V (a) and G = 1,000 V/V (b).

Figure 10: Offset-voltage change shown as a function of output voltage.

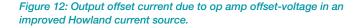

Not all op amp manufacturers specify  $A_{OL}$  the same way. TI tests its <u>precision op amps</u> for open-loop gain, which is averaged over a generous output-swing range for good linear operation (the red line in **Figure 10**). In the specifications table, it looks like **Table 2**.

When the amplifier is overdriven (creating a larger offset voltage), the output will swing closer to the rails. Sometimes output swing differs from the conditions in Table 2. The output swing in Table 3, for example, shows the output voltage with the input overdriven. My op amp development group at TI affectionately called this a "slam spec," meaning that the input is overdriven and slammed as far as it can go to the rail.

Both types of specs are useful, depending on the requirements of your application. The key is to understand and carefully interpret the specifications.

To see this original post with comments, click here.

### 5. SPICEing offset voltage: how to check the sensitivity of circuits to offset voltage

It may not always be obvious how offset voltage will affect a circuit. "Direct current (DC) offsets are easy to simulate with a simulation program with integrated circuit emphasis (<u>SPICE</u>), but <u>operational</u> <u>amplifier</u> (op amp) macromodels only predict the effects of offset voltage of one unit. What about variation from device to device?

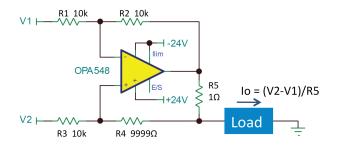

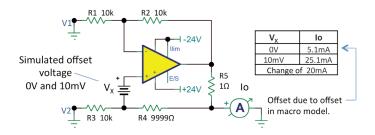

The improved Howland current-source circuit (Figure 11) provides a good example. Its feedback to both input terminals may leave you wondering how the input offset voltage ( $V_{os}$ ) of the op amp contributes to error. The <u>OPA548</u> is a hefty <u>power op amp</u> with a 5-A maximum output and 60-V supply capability. It is frequently used in Howland circuits. But how will its 10-mV maximum offset voltage affect the output current of the circuit?

Table 2: Open-loop gain specifications shown with different loads and output voltage swings.

| Output           | Conditions                 | Min | Тур  | Max | Unit |

|------------------|----------------------------|-----|------|-----|------|

| Voltage output   | $R_L = 10 \text{ k}\Omega$ | 0.2 | 0.15 | -   | V    |

| swing from rails | $R_L = 2 k\Omega$          | 0.3 | 0.2  | -   | V    |

#### Table 3: Example of an output voltage swing with the input overdriven.

Before simulating, this is an opportunity to exercise <u>best practices</u>. <u>with SPICE</u>. What do you think the output current will be with 10 mV of input offset voltage?

Offset voltage is modeled as a voltage source in series with one of the input terminals. So in SPICE, you can merely insert a DC source in series with one of the inputs to induce the effect of varying offset voltage. With V1 and V2 inputs connected to ground, ideally you would expect zero output current. But the offset voltage will supply a small input: a DC simulation with  $V_x = 0$  and  $V_x = 10$  mV. Note the change in output current due to the change in  $V_x$  (Figure 12). There may be other sources of offset, so the delta in output current from these two  $V_x$  values reveals the contribution of offset voltage. Of course, the offset could also be negative.

The output offset with  $V_x = 0$  in the simulation comes from the offset voltage (2.56 mV) included in the <u>OPA548 macromodel</u> – and would not be an additional contributor. Most of TI's macromodels have an offset voltage approximately equal to the typical offset voltage value. In some circuits, other sources of output offsets could come from input bias current and/or input offset current and would be additional contributors to total offset.

What output offset current did you predict? The improved Howland is essentially a <u>difference amplifier</u> (four resistors around an op amp) with an added resistor, R5. This unity-gain difference amplifier (equal resistors) causes the input difference voltage (V2-V1) to be impressed on R5; the resulting current flows to the load. The offset voltage, however, is applied directly to the noninverting input and is amplified by +2 – like a noninverting amplifier (G = 1 + R2/R1). Thus, a 10-mV offset voltage creates 20 mV across R5, producing a 20-mA output current offset. A -10-mV offset would create a -20-mA output current (current sinking from the load).

Maybe you see it intuitively, maybe you don't. Either way, SPICE can provide confirmation.

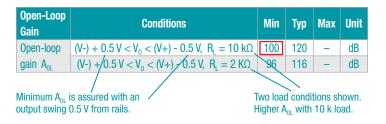

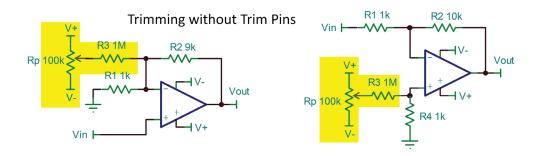

# 6. Where are the trim pins? Some background on offset-voltage trim pins

In 2012, my colleague <u>Soufiane Bendaoud</u> published an article, "<u>Pushing the Precision Envelope</u>." In it, he discussed various technologies that TI uses to "trim" or adjust the offset voltage of its amplifiers to very low values. It got me thinking about offset voltage trim pins. Where do they go?

Newer operational amplifiers (op amps) lack the offset voltage trim pins once found on virtually all op amps. There are many factors at work in this change. Better, lower-offset amplifiers, autocalibrated system designs, pressure to reduce assembly and adjustment costs, tiny surface-mount packages – all combine to reduce the use of offset trim pins. Still, many of our best-selling op amps have trim pins, and knowledge and best practices of how to use (or not use) them are fading.

This much is easy: if you do not use the trim pins, leave them open circuit, with no connection. Do not connect them to ground.

**Figure 13** shows a common type of internal trim circuitry. Trim pins connect to a tapped portion of the input-stage load circuitry. Adjusting the potentiometer skews the balance of the load plus or minus a few millivolts of input offset voltage. Datasheets generally recommend a value for the potential, but it is not critical. A much higher resistance potentiometer will cause the change in offset voltage to occur toward the extremes of rotation. Too low a value will reduce the adjustment range. Potentials in the range of +100 percent to 50 percent of the recommended value will likely function satisfactorily. Notice that the trim circuitry in this example is referenced to the V+ supply. Some op amps have trim circuitry referenced to the V- supply terminal. Connecting the wiper of the potential to the wrong rail or to ground on a dual supply will surely cause problems. Some designers attempt tricky active circuitry to drive these pins. While this is possible, ground-referenced circuitry connected to the trim pins can create power-supply rejection problems.

It is best to use the trim pins only to null the offset of the first amplifier in a signal chain. Generally, that stage has some gain and its offset dominates that of the complete signal chain. If used to correct other large sources of offset in the chain, you could introduce an unwanted temperature drift.

Lacking trim pins, there are other ways to trim offsets in your system. You could inject or sum variable voltages from a potentiometer or other control signal into various points in your signal chain. Figure 14 shows examples. The trimming voltages shown here should be derived from the power supplies. Regulated supplies are probably sufficient. Unregulated supplies, such as batteries, may not be sufficiently constant or stable.

The improved offset voltage of modern amplifiers often eliminates the need for trimming. Still, there are times when some type of offset adjustment is required. You can be ready with techniques, whether with trim pins or add-on circuitry.

Figure 13: Typical internal circuitry where trim pins connect to the input-stage load circuitry.

Figure 14: Examples of offset-correction voltages injected into various points of the signal chain.

# 7. I need high input impedance! Input impedance vs. input bias current

In helping to select <u>operational amplifiers</u> (op amps) and <u>instrumentation amplifiers</u>, I frequently hear, "I need really high input impedance." Oh, really? Are you sure?

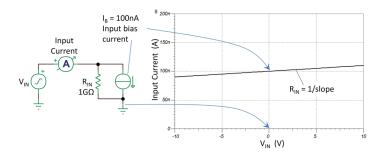

It is rare that input impedance (or more specifically input resistance) is an important issue. (Input capacitance, the reactive part of input impedance, is another matter). What is most often needed is low input bias current,  $I_B$ . Yes, they are related, but different. Let us sort it out.

A simple model of a single input is a parallel combination of a current source (the input bias current) and an input resistor (Figure 15). The resistor causes the input current to vary with input voltage. The input bias current is the input current at a specific input voltage, usually at midsupply.

The input resistance is a measure of the change in input current with a change in input voltage. It is possible to have an ampere of input bias current and still have extremely high input resistance.

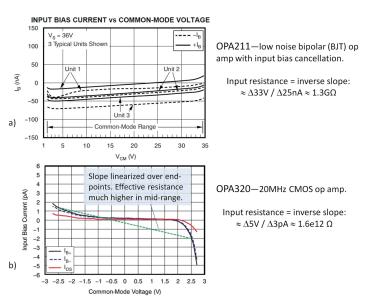

TI often provides a typical graph showing input bias current vs. common-mode voltage. A couple of examples are shown in **Figure 16**; you can see that it's not a perfectly straight line. Note that the <u>OPA211</u> is a bipolar junction transistor (BJT)-input op amp with input bias current cancellation that greatly reduces input bias current – but it is still pretty high. The OPA211's input bias current and high noise current make it an unlikely choice with a source resistance greater than 10 k $\Omega$ , so its input resistance of 1.3 G $\Omega$  is seldom an issue.

Figure 15: Model of one input terminal is a current source and an input resistor in parallel.

The <u>OPA320</u> complementary metal-oxide semiconductor (CMOS) op amp has a tiny input bias current, primarily coming from the leakage of its input electrostatic discharge (ESD) protection circuitry. These leakage currents reach a maximum near the rail voltages. CMOS and junction .(JFET)-input amplifiers are generally the best choices when you require a very low input bias current. Yes, the input resistance is high, but it is not generally an important factor in amplifier selection.

There are several ways that input bias current can be detrimental in precision-analog circuitry. Flowing through a source resistance or feedback network resistance, it can contribute  $I_B R_s$  to the offset voltage. Flowing in certain sensors and chemical cells such as pH probes, it can polarize the electrodes, creating errors and even causing permanent damage. Input bias current will charge the capacitor of an integrator circuit, creating a ramping output with zero input.

Depending on the sensitivity of your circuit to input bias current, it can be a deciding factor in amplifier selection. Check out typical performance graphs showing variations of  $I_B$  with input voltage, with an eye to the particular voltage range of interest. Overtemperature behavior may be particularly important with CMOS and JFET amplifiers, as their  $I_B$  generally rises dramatically with increasing temperature.

To see this original post, <u>click here</u>.

Figure 16: Input bias current vs. common-mode voltage.

# 8. Input bias current of CMOS and JFET amplifiers

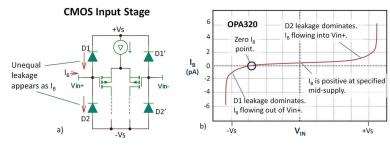

Complementary metal-oxide semiconductor (CMOS) and junction FET (JFET)-input <u>operational amplifiers</u> (op amps) are often selected for their low input bias current ( $I_B$ ). But there is more to the story than a single line in a specifications table – subtleties that you should be aware of.

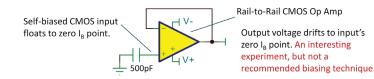

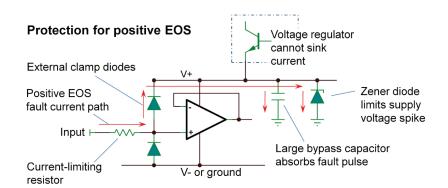

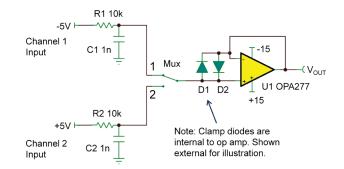

The gate of a CMOS transistor (the working input of a CMOS op amp) has extremely low input current. But these fragile gates must be protected from <u>electrostatic discharge (ESD)</u> and <u>electrical overstress</u> (EOS) with additional circuitry that is the primary source of their input bias current. This protection generally includes internal clamp diodes to the supply rails. The <u>OPA320</u> is an example, shown in **Figure 17a**. These diodes have a small leakage current in the few picoampere range. At an input voltage near midsupply rails, their leakages are pretty well-matched, leaving only a small residual difference current of less than 1 pA that appears as amplifier input bias current.

The relationship of the two diode leakages changes as the input voltage nears the supply rails. Near the bottom rail, for example, D2's reverse voltage nears zero and its leakage drops. D1's leakage will dominate, causing a higher input bias current flowing out of the input terminal. Of course, the opposite occurs as the input approaches the positive supply rail. The input bias current is specified and tested at the midpoint, where leakage is nearly matched and quite low.

The result is an input bias current versus an input voltage that varies, as shown in **Figure 17b**. For any given unit, there is an

input voltage where the input bias current is zero (assuming no significant package or circuit layout leakage). In fact, with a rail-torail op amp you can often self-bias the input (Figure 18); the output will drift to a voltage equal to the zero input-bias-current point. It is an interesting experiment but not a particularly useful circuit.

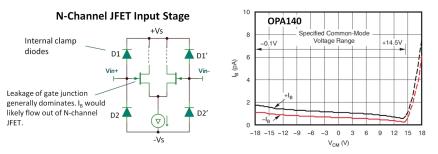

The story can be different with JFET-input amplifiers such as the <u>OPA140</u> (Figure 19). Here, the gate of the input transistor is a diode junction and its leakage current is often the dominant source of input bias current. The input gate junction is generally larger and therefore leakier than the protection diodes. Thus, the input bias current is more often unidirectional. It can vary and depends on the amplifier.

So, what to conclude? If very low input bias current is important in your circuit, be aware. Look carefully at typical performance graphs to glean all available information. If you operate with input voltages that are near the positive or negative rails, you may have higher input bias current. This leads to another important point – input bias current will increase significantly with temperature.

This discussion applies to most common general-purpose CMOS and JFET amplifiers, but there are special-purpose amplifiers designed for ultra-low input bias current. They use creative protection circuitry with unique pinouts to achieve  $I_B$  in the range of 3 fA – three orders of magnitude lower than general-purpose devices.

Examples:

- The LMP7721 3-fA input bias current CMOS op amp.

- The INA116 ultra-low input bias current instrumentation amplifier.

Figure 17: Protecting op amps from ESD and EOS using internal clamp diodes to the supply rail (a); input bias current versus input voltage (b).

Figure 19: Input bias current is often unidirectional depending on the input amplifier, such as with the JFET-input amplifier shown here.

## 9. Temperature effects on input bias current

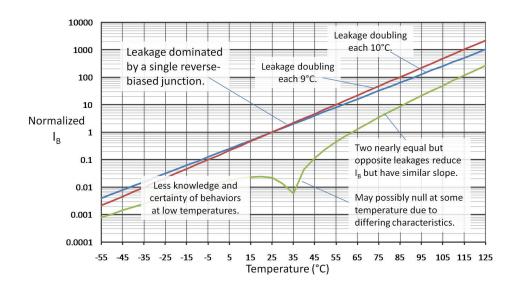

In <u>section 8</u>, I looked at the source of input bias current in complementary metal-oxide semiconductor (CMOS) and junction FET (JFET) amplifiers, finding that it comes from the leakage of one or more reverse-biased P-N junctions. I ended with a caution that these leakages increase significantly with temperature.

The reverse-biased leakage of a P-N junction has a strong positive temperature coefficient, approximately doubling for each 10°C increment in temperature. This exponential increase racks up quickly, as shown in the normalized graph of Figure 20. At 125°C, leakage climbs to approximately 1,000 times the room-temperature value.

The rate of increase can vary with diode characteristics, and the doubling of current may occur over a range of 8°C to 11°C. This increased bias current at high temperatures can be a significant problem in some circuits and may be a good reason to select a FET or CMOS <u>operational amplifier</u> (op amp) with a very low room temperature input bias current. In some cases, you may achieve lower  $I_B$  at high temperatures with a bipolar-input (BJT) op amp that does not have such a dramatic increase at high temperature.

The leakage generally continues to fall at lower temperatures, but other possible sources of leakage may alter the behavior. These stray leakages may have different temperature dependencies. To be honest, less is known about the behavior below room temperature because the higher leakage at room temperature and above is the greater concern. It is best not to place high confidence in behavior much below room temperature. The important issue at low temperatures is more likely to be possible water condensation, which can cause leakage to rocket upward.

As discussed in <u>section 8</u>, the input bias current of most CMOS op amps comes from the difference in leakage of two input-clamp diodes connected to the power rails. In a perfectly balanced world, the residual difference between two nearly equal leakages still has

the same exponential temperature variation; it just starts at a lower initial value. The polarity of  $I_B$  is uncertain; and, with small differences in diode behavior, the net current may dip through zero at some temperature (the logarithmic graph shows the absolute value without a sign).

So, what to conclude? If very low input bias current is critical in your FET op amp circuit, carefully consider its increase with temperature. Study all of the specifications and typical performance graphs. Avoid placing sensitive circuitry near heat sources. Make your own measurements, if necessary. For really critical applications, there are special-purpose amplifiers with ultra-low input bias current. They use creative protection circuitry with unique pinouts to achieve  $I_B$  in the range of 3 fA at room temperature – three orders of magnitude lower than general-purpose devices.

Examples:

- The LMP7721 3-fA input-bias-current CMOS op amp.

- The INA116 ultra-low-input-bias-current instrumentation amplifier.

To see this original post with comments, click here.

A random quiz: On the film capacitors in **Figure 21**, what is the meaning and purpose of the black bands?

See Page 36 for the answer to this quiz.

Figure 21: Film capacitors—what is the purpose of the marking stripe?

Figure 20: Reverse-biased leakage of a P-N junction approximately doubles with each 10°C increment in temperature.

# 10. Input bias current cancellation resistors: do you really need them?

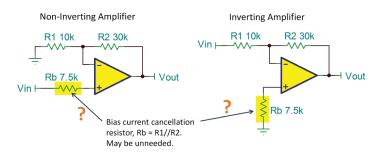

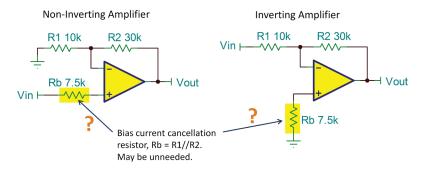

Do you add a resistor to match the direct current (DC) resistance at the inputs of your <u>operational amplifier</u> (op amp) circuits? Check the circuits in **Figure 22**. Many of us were instructed to add Rb as "good practice," making its value equal to the parallel combination of R1 and R2. Let us look at the reason for this resistor and consider when it is appropriate and when it is not.

Figure 22: Resistor added to non-inverting input to match the source resistances.

The purpose of Rb is to reduce the voltage offset caused by the input bias current. If both inputs have the same input bias current, equal current flowing through equal resistances will create equal and opposite offset voltages. Thus, input bias current will not contribute to the offset voltage of the circuit. The basic idea has merit in some instances. But before adding Rb, is it always necessary?

Many times, the parallel resistance of R1 and R2 is low enough, and input bias current is low enough, that the offset created without Rb is insignificant. Before adding this resistor, calculate the error. Let us assume for this application that the input bias current of the op amp is 10 nA. Without using Rb, the input-referred offset voltage due to the input bias current will be:

Input offset voltage due to  $I_B = (10 \text{ nA}) (7.5 \text{ k}\Omega) = 75 \text{ }\mu\text{V}$  (1)

Will 75  $\mu$ V of input offset affect your circuit? Many times the answer will be no, so why add the resistor?

Consider the offset voltage of the op amp you are using. It may be pointless to be concerned with 75  $\mu$ V if, for example, the offset-voltage specification of your op amp is 1 mV. So compare the error produced by the input bias current to the offset-voltage specification before routinely adding Rb to your circuit.

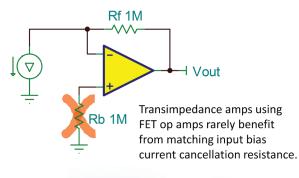

Transimpedance applications often use high feedback-resistor values to amplify very small currents (Figure 23). Here again, you may be tempted to add Rb to balance the resistance at both inputs. But these applications generally use FET- or complementary metal-oxide semiconductor (CMOS)-input op amps. With their very low input bias current, the offset error is generally very small.

Thermal noise produced by Rb and possible external noise pickup at this high-impedance node may be additional reasons to eliminate Rb. With minimal error from the input bias current, why add possible noise to the circuit?

There may occasionally be a clear and valid case for using a bias current cancellation resistor. But many circuits derive no significant benefit, and may even suffer reduced performance.

To see this original post, <u>click here</u>.

#### Transimpedance Amplifier

Figure 23: High gain transimpedance circuits using FET op amps should omit the Rb balancing resistor.

# 11. Internal input bias current cancellation of bipolar op amps

In <u>section 10</u>, I reviewed the use of an input-bias-current cancellation resistor to balance the source resistance at the two inputs of an <u>operational amplifier</u> (op amp). I concluded that this practice is often not necessary and may even be detrimental.

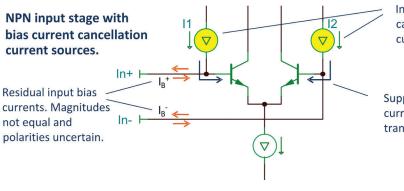

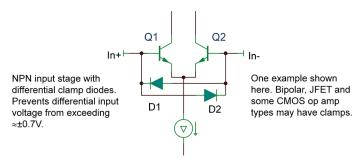

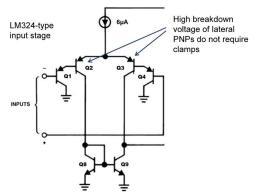

I ended the previous section by saying that there are certain op amps for which this practice is definitely not recommended: amplifiers with bipolar input transistors that have internal input bias current cancellation. Their current sources, I1 and I2, supply base current for the input transistor pair (Figure 24). These currents are derived by mirroring carefully matched base currents into the op amp's input terminals.

While these currents are accurately matched to the base current of the input transistor (typically within a few percent), they are not perfect. They leave a small residual input bias current that could be positive or negative. The residual current may be quite different on the two input terminals. They may even be opposite polarities. Any possible benefit from matching source resistance (as in **Figure 25**) relies on nearly matching input bias currents. Internal input bias current cancellation renders this practice useless.

Which op amps have input bias current cancellation? Datasheets sometimes do not make this feature apparent. The effects are generally revealed, however, in the details of input-bias-current specifications.

Figure 26a shows the input-bias-current specification for the <u>OPA209</u>, a low-noise op amp with input-bias-current cancellation. Note that the input bias current is preceded by a  $\pm$  symbol to indicate that current could flow in either direction, your first hint. Also note that the specifications for input offset current are the same magnitude as the input bias current (actually identical on this op amp). These specifications reveal that this device has internal input bias current cancellation.

**Figure 26b** shows a hypothetical specification for the OPA209, assuming it did not have bias current cancellation. Note the much larger input bias current. And now, the input offset current is much smaller than the input bias current because the two input bias currents are nearly equal. Depending on the circuit and application, this hypothetical op amp might benefit from the use of a bias current cancellation resistor, as shown in **Figure 24**.

Internal input bias current cancellation is generally found on precision and low-noise op amps with input from bipolar junction transistors (BJTs) – ones that would otherwise have an uncomfortably high input bias current. Internal cancellation makes these amplifiers useful in a wider range of circuits.

Do you ever design circuits that rely on a known polarity of input bias current? It would not be wise with these canceled-input devices, right?

To see this original post with comments, click here.

Figure 24: BJTs with internal current sources for input bias current cancellation.

Figure 25: Op amp circuit with bias-current-cancellation resistor added to non-inverting input.

Input bias current cancellation current sources.

Supplies base current for input transistors.

# Input bias current specification for OPA209 (has input bias current cancellation).

| Input Bias Current             | Min | Тур  | Max       | Unit       |

|--------------------------------|-----|------|-----------|------------|

| Input bias current             |     | _±1  | ±4.5      | nA         |

| Input offset current           | /   | ±0.7 | ±4.5      | <b>n</b> A |

|                                | /   |      |           |            |

| ± Indicates bias current could |     |      | et curren |            |

(a)

flow in either direction.

Input offset current same or similar to input bias current.

# Hypothetical specification for same op amp assuming no bias compensation.

| Input Bias Current                        | Min  | Тур                  | Max                    | Unit |

|-------------------------------------------|------|----------------------|------------------------|------|

| Input bias current                        |      | 40                   | 80 、                   | nA   |

| Input offset current                      |      | 1.5                  | 5                      | nA   |

| Offset current, los = $(L_B^+) - (L_B^-)$ | Inpu | it offset cu<br>than | rrent muc<br>input bia |      |

(b)

Figure 26: Specifications of an op amp with input-bias-current cancellation (a); and a similar op amp without input-bias-current cancellation (b).

# Chapter IV: Stability and Oscillations

# 12. Why op amps oscillate: an intuitive look at two frequent causes

Bode plots are great analytical tools, but you may not find them intuitive. This is a purely qualitative look at frequently encountered causes for <u>operational amplifier</u> (op amp) instability and oscillations.

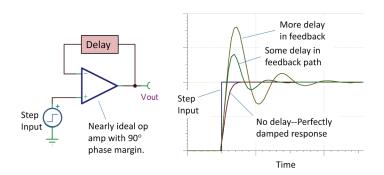

The perfectly damped response in Figure 27 occurs with no delay in the feedback signal reaching the inverting input. The op amp responds by ramping toward the final value, gently slowing down as the feedback signal detects closure on the proper output voltage.

# Figure 27: Op amp step response with varying delay inserted in the feedback path.

Problems develop when the feedback signal is delayed. With delay in the loop, the amplifier does not immediately detect its progress toward the final value. It overreacts by racing too quickly toward the proper output voltage. Note the faster initial ramp rate with delayed feedback. The inverting input fails to receive timely feedback that it indeed reached and passed the proper output voltage. It overshoots its mark and requires several successively smaller polarity corrections before finally settling.

A little delay and you merely get some overshoot and ringing. Too much delay and these polarity corrections continue indefinitely – an oscillation.

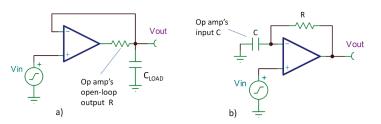

The source of delay is often a simple low-pass resistor-capacitor (RC) network. OK, it is not a constant delay for all frequencies, but the gradual phase shift of this network from 0° to 90 degrees produces a first-order approximation of time delay,  $t_d$  = RC.

Figure 28: Phase shift (delayed feedback) commonly occurs in two ways: Due to capacitive load (a); or with capacitance at the inverting input terminal (b).

There are two commonly encountered situations where this RC network unintentionally sneaks into circuits. The first is with a capacitive load (Figure 28a). The resistor is the op amp's open-loop output resistance. The capacitor is, of course, the load capacitance.

In the second case (Figure 28b), the feedback resistance and the op amp's input capacitance form the RC network. Circuit-board connections also contribute to the capacitance at this sensitive circuit node. Note that the two circuits have identical feedback loops. The only difference is the node at which the output is taken. From a loop-stability standpoint, they can create the same issues. And these two causes of delayed feedback often occur in combination – a bit of both can be double trouble.

The second case needs a bit more comment: A feedback resistor is not necessary for the simple G = 1 buffer, so the more common situation is a gain configuration using a feedback resistor and resistor to ground (**Figure 29**). The parallel combination of these resistors forms the effective R in the RC circuit.

Figure 29: The parallel resistance of the feedback network form the R in an RC circuit.

There is more to learn with Bode analysis of feedback amplifiers. Still, this simple, intuitive view of how delay or phase shift in the feedback path affects stability can help you diagnose and solve the most common stability problems.

### 13. Taming the oscillating op amp

In <u>section 12</u>, I looked at two very common reasons for oscillations or instability in <u>operational amplifier</u> (op amp) circuits. The ultimate cause of both was delay or phase shift in the feedback path.

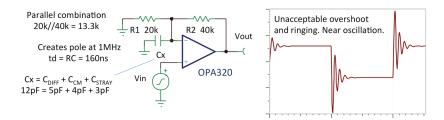

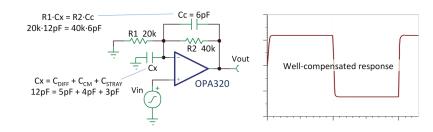

A simple noninverting amplifier can be unstable or have excessive overshoot and ringing if the phase shift or delay created by the op amp's input capacitance (plus some stray capacitance) reacting with the feedback network resistance is too great (**Figure 30**). You may be able to make some improvements by reducing stray capacitance at this node, minimizing the circuit-board trace area of this connection. For a given op amp, input capacitance (differential plus common-mode capacitance) is a fixed value – you are stuck with it. You can, however, reduce the resistances of the feedback network proportionally to keep the gain identical.

Reducing the resistances moves the pole created by this capacitance to a higher frequency and decreases the delay time constant. Reducing the resistances to 5 k $\Omega$  and 10 k $\Omega$  in this example is a big improvement but still produces approximately 10-percent overshoot with ringing. It also creates additional load on the op amp, so you cannot take this solution too far. The sum of the two resistors is a load on the op amp, and you would not want it to be too low.

The better solution is likely to be a capacitor, Cc, connected in parallel with R2 (Figure 31). When  $R1 \times Cx = R2 \times Cc$ , the voltage divider is compensated and the impedance ratio is constant for all frequencies. There will be no phase shift or delay in the feedback network.

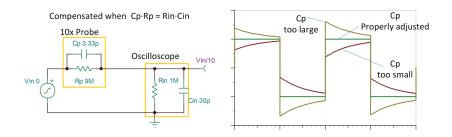

You can liken the feedback network to the compensated attenuator in a 10-times oscilloscope probe (Figure 32). It is the same concept. A variable capacitor in the probe allows adjustment to make the two time constants equal. Note that the response of this scope probe does not ever appear unstable, even when improperly adjusted. Why? Because it is not inside a feedback loop.

Just as you can adjust one of the capacitors in a scope probe to fine-tune the compensation, you may also need to adjust the value of Cc shown in **Figure 31**. You may not precisely know the capacitance, Cx, due to the uncertain effects of stray capacitance. Furthermore, you may want to tune the response of the circuit to meet your requirements, with a little bit of overshoot for improved speed and bandwidth.

Another common cause of instability is an op amp with capacitive load. Again, this situation produces phase shift in the loop (delayed feedback) that is the root of the problem. This one is tricky because open-loop output resistance is internal to the op amp. You cannot connect a compensating capacitor across this resistor. In fact, it is not really a resistor at all; it is an equivalent output resistance of the op amp circuitry.

Consider your last oscillating op amp. Can you explain the problem with delayed feedback?

To see this original post with comments, click here.

Figure 30: Excessive output overshoot and ringing indicates possible instability.

Figure 31: A capacitor, Cc, connected in parallel with R2 avoids phase shift in the feedback signal path.

Figure 32: A feedback network is much like a compensated attenuator in a 10x oscilloscope probe.

# 14. Taming oscillations: the capacitive load problem

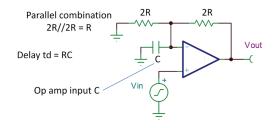

I have been looking at the stability of <u>operational amplifiers</u> (op amps), considering how phase shift (or call it delay) in the feedback path can cause problems. Picking up from <u>section 12</u> and <u>section 13</u>, stability with a capacitive load is a tricky case.

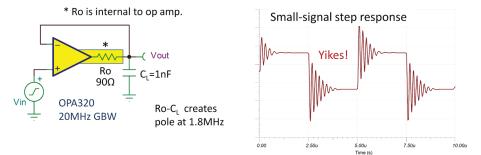

The troublemaker, the open-loop output resistance (Ro) of the op amp, is not actually a resistor inside the op amp. It is an equivalent resistance dependent on the internal circuitry of the op amp. There is no chance to change it without changing the op amp.  $C_{L}$  is the load capacitance. If you want to drive a certain  $C_{L}$ , you are stuck with the pole created by Ro and  $C_{L}$ . A 1.8-MHz pole inside the feedback loop of a 20-MHz op amp in G = 1 spells trouble. Check it out in Figure 33.

Solutions to this issue have a common theme – they slow the amplifier down. Think about it: The loop has a fixed amount of delay, from Ro and  $C_L$ . To accommodate this delay, the amplifier must respond more slowly so that it does not speed past, overshooting a desired final value.

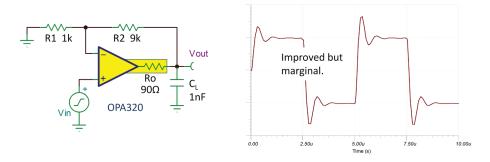

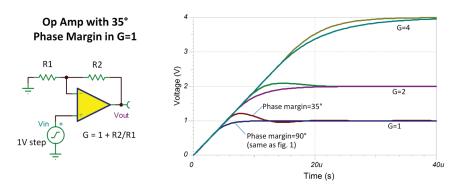

A good way to slow things down is to put the op amp in a higher gain. Higher gain decreases the bandwidth of the closed-loop amplifier. Figure 34 shows the <u>OPA320</u> driving the same 1-nF load but in a gain of 10. The response to a small step dramatically improves but is still marginal. Increase the gain to 25 or more, and it would look pretty good.

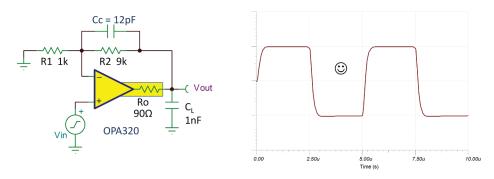

But here is another trick. **Figure 35** is still a gain of 10 but with Cc added, slowing things down a bit more in just the right way. Not enough Cc and the response looks more like **Figure 34**. Too much Cc and you are headed for trouble, more like **Figure 33**.

Getting this compensation just right is solving a "rate-of-closure" issue – Bode analysis. A bit of intuition is helpful with these problems, but if you want to advance to the next level of phase-compensation competence, you need Mr. Bode.

My colleagues, <u>Pete Semig and Collin Wells</u>, did a great job distilling the subject of op amp stability and Bode analysis to its essence.

To see this original post with comments, click here.

Figure 33: A 1.8-MHz pole inside the feedback loop of a 20-MHz op amp in G = 1 (left) can result in an undesirable small-signal step response (right).

Figure 34: Using an op amp in a higher gain of 10 decreases the bandwidth of the closed-loop amplifier; however, the improvement is marginal.

Figure 35: Using the same configuration, adding a Cc of 12 pF in parallel with the feedback resistor produces an ideal response.

### 15. SPICEing op amp stability

The simulation program with integrated circuit emphasis (SPICE) is a useful tool to help check for potential circuit-stability problems. Here is one simple way to do it.

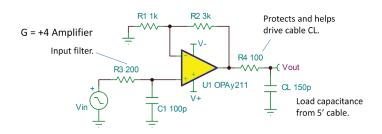

**Figure 36** shows a noninverting amplifier using the <u>OPA211</u> with a couple of minor variations common in many applications. R3-C1 is an input filter. R4 is an output resistor to protect against abuse when connected to the outside world.  $C_{L}$  models a five-foot cable.

# Figure 36: A noninverting amplifier with minor variations common to many applications.

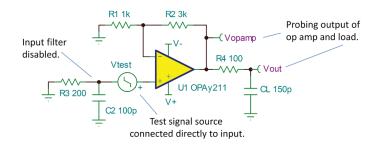

Checking the response to a small-signal step function or square wave is the quickest and easiest way to look for possible stability problems. Figure 37 shows the simulation circuit. Notice that the input terminal is connected to ground and the input test signal is connected directly to the noninverting input. The input filter would slow the input edge of a step function. If you want to know how a bell rings, hit it with a hammer, not a rubber mallet.

The response is probed at the output of the <u>operational amplifier</u> (op amp), not just the V<sub>OUT</sub> node of the circuit. R4 and C<sub>L</sub> filter the output response so that V<sub>OUT</sub> will not show the true overshoot of the op amp. To check stability, you want to know what the op amp is doing.

#### Figure 37: A simulation circuit with the input terminal connected to ground and the input test signal connected directly to the noninverting input.

Notice that the amplitude of the applied step is 1 mV (creating a 4-mV step at the output). You want the small-signal step response. A large input step that induces slewing will have less overshoot and will not clearly reveal potential instability.

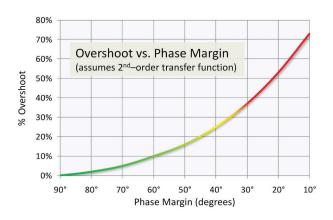

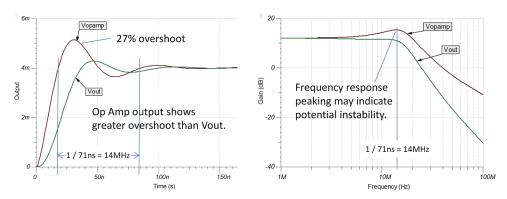

The simulation shows approximately 27-percent overshoot at the op amp's output – too much for you to be comfortable that this circuit will be stable under all conditions (Figure 38).

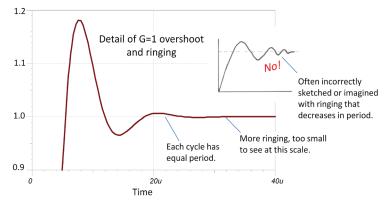

Assuming a second-order stability system, this overshoot would indicate a phase margin of approximately 38 degrees. Also notice that the frequency response shows considerable amplitude peaking, another sign of potential instability. The peaking occurs at 14 MHz – the inverse of the period of the ringing in the time domain. A commonly accepted guideline for reasonable stability is a phase margin of 45 degrees (or greater), which translates to 20-percent (or less) overshoot (Figure 39).

# Figure 39: A 20-percent overshoot indicates approximately 45° phase margin—often considered to be satisfactory for most circuits.

There are fancier analyses that you can do with SPICE – Bode analysis by breaking the loop, finding phase and gain margins. But for most relatively simple circuits (a feedback loop involving one op amp), this approach is a very good indicator of possible problems.

Of course, any SPICE simulation relies on the accuracy of the op amp's macromodel. Our best SPICE models are excellent but not perfect. Furthermore, circuit variation, nonideal components, circuitboard layout parasitics, poor supply bypassing – all can affect the circuit. That's why you build it, test it, compare with simulations and optimize. SPICE is a useful tool, valuable but not perfect.

The late <u>Bob Pease</u>, a true analog guru, wrote skeptically about the use of SPICE. Check out this blog on his opinions: <u>SPICE It Up! ... but does Bob Pease say no?</u> To see this original post with comments, <u>click here</u>.

Figure 38: An op amp circuit with 27-percent overshoot may be marginally unstable.

## 16. Input capacitance: Common mode? Differential? Huh?

The input-capacitance specifications of <u>operational amplifiers</u> (op amps) are often confused or ignored. Let us clarify how to best use these specifications.

The input capacitance at the inverting input can affect the stability of an op amp circuit by causing phase shift – a delay of the feedback reaching the inverting input. The feedback network reacts with the input capacitance to create an unwanted pole. Scaling the impedance of the feedback network in relation to the input capacitance is an important step to assure a stable amplifier circuit. But which capacitance matters – differential? Common mode? Both?

The input capacitance of an op amp is generally found in an input-impedance specification showing both differential and common-mode capacitance (Table 4).

#### **OPA1652**

| Input Impedance | Min | Тур      | Max | Units    |

|-----------------|-----|----------|-----|----------|

| Differential    | _   | 100 //6  |     | ΜΩ // @₽ |

| Common-Mode     |     | 6000 //2 |     | GΩ // OF |

# Table 4: Input-impedance specification showing both differential and common-mode capacitance.

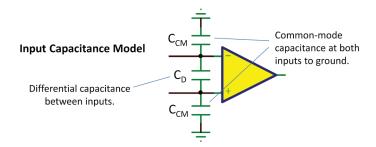

Input capacitance is modeled as common-mode capacitance from each input to ground and differential capacitance between the inputs; see **Figure 40**. Though there is no ground connection on an op amp with dual supply voltages, consider the common-mode capacitances as being connected to the V– supply terminal, the alternating current (AC) equivalent of ground.

Figure 40: Input capacitance modeled as common-mode capacitance from each input to ground and differential capacitance between the inputs.

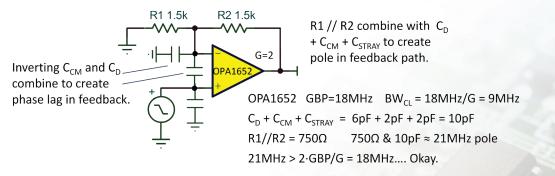

Figure 41: Calculation of pole due to input capacitance and feedback network.

At high frequencies where stability is a concern, the op amp has little open-loop gain, and substantial AC voltage exists between the two inputs. This causes the differential capacitance to combine with the inverting common-mode capacitance to alter the phase of the feedback signal. So add the two capacitances that connect to the inverting input. Include an estimate of stray wiring capacitance (perhaps around 2 pF). This total capacitance reacts with the parallel impedance of the feedback network (R1//R2) to create a pole (Figure 41).

A guideline: The frequency of this pole should be greater than two times the closed-loop bandwidth of the amplifier. A pole at two times the closed-loop bandwidth will reduce the phase margin of the circuit by approximately 27°. This is generally OK for most circuits in a closed-loop gain of two or greater. Applications with critical settling requirements or capacitive loads may require even greater margin. Reduce the feedback network impedance or consider adding a <u>capacitor across the feedback capacitor, R2</u>.

Today's <u>general-purpose op amps</u> often have wider bandwidths, from 5 MHz to 20 MHz and more. Feedback network resistances that may have been OK with 1-MHz op amps can now create problems – a reason to be diligent when checking the stability of your designs.

<u>SPICE simulation</u> is very helpful in checking sensitivities to input capacitance and feedback impedance, and good op amp macromodels accurately model input capacitances. A <u>transient</u> <u>response check</u> with a 1-mV input step should not cause excessive overshoot and ringing. But remember: Reality always trumps guidelines and simulations. This type of circuitry may require fine-tuning in a final circuit layout.

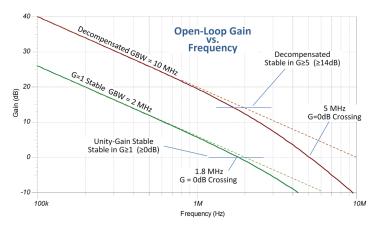

## 17. Op amps ... G = 1 stable and decompensated

Unity-gain-stable <u>operational amplifiers</u> (op amps) are stable in the common G = +1 configuration, returning 100 percent of the output signal back to the inverting input. While it would be incorrect to call this truly a "worst case" for stability, you could reasonably call it a very common, testy case.

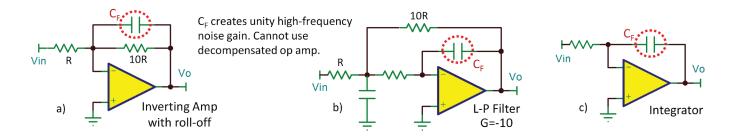

Decompensated op amps have smaller compensation capacitors that yield wider gain bandwidth (GBW) and faster slew rates. While higher speed normally demands more power, the same basic op amp can be significantly faster while operating on the same current. But they are not unity gain stable – they must be used in <u>noise gains</u> significantly greater than unity.

**Figure 42** shows the critical portion of a gain vs. frequency graph for an idealized pair of unity-gain-stable and decompensated op amps. The decompensated version has five times the GBW – 10 MHz vs. 2 MHz. Slew rate gets the same boost. Note that the unity-gain bandwidth of the unity gain stable op amp is slightly less than its GBW, a common behavior. The unity-gain bandwidth of the decompensated amplifier is half its GBW. You have no business operating this amplifier with noise gain near the unity-gain bandwidth because a second pole at 3 MHz greatly affects the gain/phase behavior in this region. Phase margin would be poor or nonexistent.

Figure 42: Graph of open-loop gain versus frequency for an idealized pair of unity-gain stable and decompensated op amps.

Decompensated op amps seem to hold a certain mystery, leaving some users uncertain about whether their circuits will be stable. **Figure 43a** shows a common misstep. Although this amplifier is connected in a signal gain of -10, a feedback capacitor rolls off the response at high frequency. This capacitor can be a virtual short circuit at high frequency where stability issues are a concern – unity gain. It is OK to use a small feedback capacitor to <u>compensate</u> the feedback network for flat gain, but a larger cap that rolls off response is sure to create problems.

Likewise, the multiple-feedback filter in **Figure 43b** invites trouble regardless of the low-frequency gain of the filter. The integrator (**Figure 43c**) is yet another application not suited to decompensated op amps.

TI has improved its op amp designs. We are smarter now and we have much better integrated circuit (IC) processes. With a few hundred microamperes, we can now make an amplifier that once required a couple of milliamperes. So sometimes a modern unity-gain-stable op amp may come very close to, or even beat, the speed/power of an older decompensated amp. Still, a decompensated op amp may be the best solution for a demanding application.

Let me be clear, I am not trying to urge you to select decompensated op amps over unity-gain-stable op amps. Each has merits, and you get to "vote" with your design choices. Whatever your selection, you should clearly understand the differences and issues. If you are unsure, help is available in the <u>Precision Amplifiers</u> forum on TI's E2E Community.

Here are some examples of decompensated and unity-gain-stable op amp pairs:

- <u>OPA228</u> (OPA227 unity-gain-stable version) precision, low-noise, bipolar junction transistor (BJT) op amp.

- <u>OPA637</u> (OPA627 unity-gain-stable version) precision, high-speed, junction FET (JFET) op amp.

- <u>OPA345</u> (OPA344 unity-gain-stable version) rail-to-rail, CMOS op amp.

- LMP7717 (LMP7715 unity-gain-stable version) 88-MHz, CMOS op amp.

Figure 43: Using a decompensated op amp with a feedback capacitor to roll off the response at high frequency can lead instability (a); a multiple-feedback filter encounters problems irrespective of the filter's frequency gain (b); and an integrator is also unsuitable for decompensated op amps

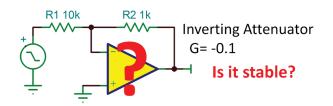

# 18. The inverting attenuator G = -0.1: is it unstable?

Unity-gain-stable <u>operational amplifiers</u> (op amps) are stable in a gain of one or greater, but not less, right? What to do (Figure 44)?

Figure 44: Example of an inverting attenuator.

OK, here is the short answer: an inverting attenuator is stable! You want to know why, right? There are a couple of ways to look at this issue, and a quick look may add clarity to general stability issues.

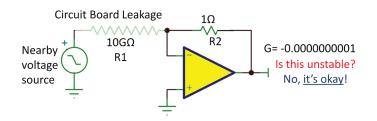

Consider this: If G = -0.1 were unstable, then even lower gain should be worse, right? Let us draw a circuit: a unity-gain amplifier with a  $1-\Omega$  feedback resistor, shown in **Figure 45**. Then consider possible circuit-board leakage forming an input resistor, R1 = 10G $\Omega$ . This is a stray "input signal" amplified at very low inverting gain. Is it unstable? Certainly not! It is just a unity gain buffer with virtually no input. Stable.

Figure 45: A unity-gain amplifier circuit with a 1- $\Omega$  feedback resistor is stable.

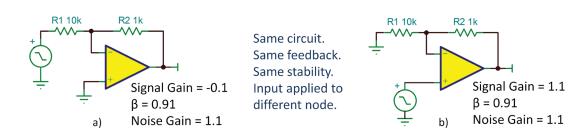

Think of the stability of an op amp as related to how much output signal is fed back to the inverting input. Stability experts refer to this feedback factor as beta ( $\beta$ ). In unity gain, 100 percent of the output voltage is returned to the inverting input, so  $\beta$  is one. The example in **Figure 45** is essentially the same with nearly all of the output signal fed back to the inverting input.

Figure 46a shows an inverting amplifier and Figure 46b shows a noninverting amplifier. The circuits are the same; the input signal is just applied to different nodes. Both circuits return the same amount of output signal to the inverting input so their stability behavior is the same.  $\beta$  is the same.

Op amp wonks also use the term "noise gain" – so named because the op amp's voltage noise is amplified to the output by this factor. It is just another way to quantify the amount of feedback. An op amp circuit prone to oscillations or instability is incited by its own internal noise, amplified and fed back to the inverting input. The inverting amplifier, **Figure 46a**, has the same noise gain,  $\beta$ , and therefore the same stability behavior as its noninverting cousin, even though the input signal gain is different.

Are there circuits with noise gains less than one? Is  $\beta$  ever greater than one? Noise gains less than unity and  $\beta$  greater than one occur when gain is included in the feedback loop. Multiple amplifiers in a larger feedback loop, such as a control system, can face this issue. It also occurs when a transistor (common-emitter or common-source configuration) is included inside the feedback loop of an op amp. These circuits can have tricky stability problems.

Of course, there are other possible causes of oscillations or instability in an inverting attenuator. Capacitive load, excessively high resistor values or too much capacitance at the inverting input can cause instability – but these are unrelated to the basic inverting-attenuator configuration. Misconceptions about the "dangers" of the inverting attenuator persist. Relax. <u>Simulate stability</u> in <u>TINA-TI</u> <u>software</u> or your favorite SPICE program to confirm it. And if you have doubts or problems, check with the experts in the <u>Precision</u> <u>Amplifiers forum</u> on TI's E2E Community.

Figure 46: These two circuits, an inverting amplifier (a) and noninverting amplifier (b) have the same feedback factor and stability issues, but with the input signal are applied to different nodes.

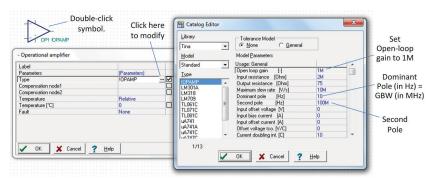

# 19. Simulating gain bandwidth: the generic op amp model

It may not always be obvious how the gain-bandwidth product (GBW) of an <u>operational amplifier</u> (op amp) may affect your circuits. Macromodels have a fixed GBW. Though you can look inside these models, it is best not to tinker with them. What to do?

You can use a generic op amp model in the simulation program with integrated circuit emphasis (SPICE) to check your circuits for sensitivity to GBW. Most SPICE-based circuit simulators have a simple op amp model that you can easily modify. **Figure 47** shows one in <u>TINA-TI software</u>.

#### Figure 47: Using TINA-TI software to create a generic op amp model in SPICE to check circuits for sensitivity to GBW.

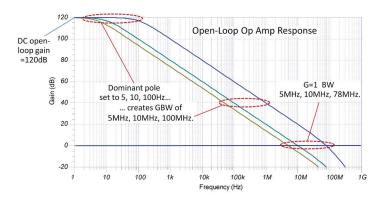

First, set its direct current (DC) open-loop gain to 1 M (120 dB). Then, a dominant pole frequency (entered in hertz) will create a GBW of the amplifier in megahertz. In this example, a 10-Hz dominant pole creates a GBW of 10 MHz. **Figure 48** shows the open-loop response for three different GBWs: 5 MHz, 10 MHz and 100 MHz.

Figure 48: Open-loop response with GBWs of 5 MHz, 10 MHz and 100 MHz.

Note that this simple model also includes a second pole (some folks call it a nuisance pole). In some cases, you may want to make this second pole a very high frequency, such as 10 GHz. This will create an ideal 90 degrees phase margin for any reasonable GBW. In this example, I set the second pole at 100 MHz, equal to the highest GBW that I am simulating. You can see the effect of this second pole in the 100-MHz GBW response, causing the open-loop response to bend downward at 100 MHz. It causes the unity-gain bandwidth to pull in to approximately 78 MHz, similar to what you might see with a real op amp of this GBW. Unity-gain bandwidth and GBW of a real op amp are not necessarily the same number.

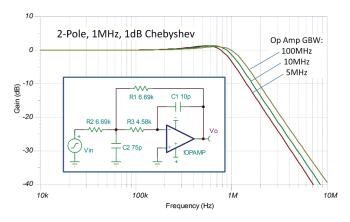

Active filter designs can be tricky to judge GBW requirements and are a good case for using this technique. <u>WEBENCH® Filter Designer</u>, used to design the Chebyshev filter in Figure 49, provides GBW recommendations, but its guidelines may be more stringent than needed in some circumstances. For this design, it recommends a 100-MHz or greater GBW to achieve nearly ideal filter-design characteristics. I simulated the design using the three GBWs shown in Figure 48: 5 MHz, 10 MHz and 100 MHz. With these results, you might decide that a GBW less than 100 MHz could be satisfactory. For final simulations, you should use the macromodel for the op amp you select.

Figure 49: A Chebyshev filter designed in WEBENCH Filter Designer software, but GBW may be more stringent than necessary.

I used the parameter-stepping function in TINA-TI software, varying the dominant pole to change the GBW. Other simulators have similar capability. Of course, you could change parameters manually, too. Either way, varying the GBW of a generic op amp model will give you some insight on its effect in your circuits.

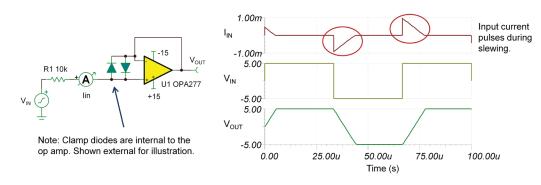

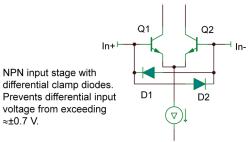

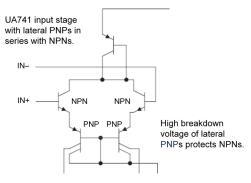

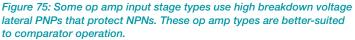

### 20. Slew rate: the op amp speed limit

Slewing behavior of <u>operational amplifiers</u> (op amps) is often misunderstood. It is a meaty topic, so let us sort it out.

The input circuitry of an op amp circuit generally has a very small voltage between the inputs – ideally zero, right? But a sudden change in the input signal temporarily drives the feedback loop out of balance, creating a differential error voltage between the op amp inputs. This causes the output to race off to correct the error. The larger the error, the faster it goes; that is, until the differential input voltage is large enough to drive the op amp into slewing.

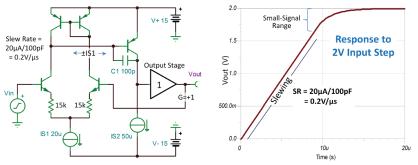

If the input step is large enough, the accelerator is jammed to the floor. More input will not make the output move faster. (Figure 50 shows why in a simple op amp circuit.) With a constant input voltage to the closed-loop circuit, there is zero voltage between the op amp inputs. The input stage is balanced, and the current IS1 splits equally between the two input transistors. With a step-function change in  $V_{IN}$  greater than 350 mV for this circuit, all of the IS1 current is steered to one side of the input transistor pair. That current charges (or discharges) the Miller compensation capacitor, C1. The output slew rate (SR) is the rate at which IS1 charges C1, equal to IS1/C1.

Figure 50: A large change in the input signal creates an output slewing condition.

There are variations, of course. Op amps with slew enhancement add circuitry to detect this overdriven condition and enlist additional current sources to charge C1 faster – but they still have a limited slew rate. The positive and negative slew rates may not perfectly match. They are close to equal in this simple circuit, but this can vary with different op amps. The voltage needed to slew an input stage (350 mV for this design) varies from approximately 100 mV to 1 V or more, depending on the op amp.

While the output is slewing, it cannot respond to incremental changes in the input. The input stage is overdriven and the output rate-of-change maxes out. But once the output voltage nears its final value, the error voltage across the op amp inputs reenters the linear range. Then the rate of change gradually reduces to make a smooth landing at the final value.

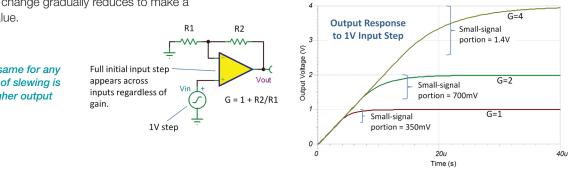

Figure 52: The slew rate is the same for any closed-loop gain but the onset of slewing is more gradual and occurs at higher output voltage in higher gains.

Figure 51: A sine wave shown accurately reproduced (top) and at the onset of slewing (bottom).

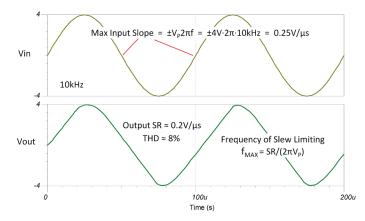

There is nothing inherently wrong with slewing an op amp – no damage or fines for speeding. But to avoid gross distortion of sine waves, you should limit the signal frequency and/or output amplitude so that the maximum slope does not exceed the amplifier's slew rate. Figure 51 shows that the maximum slope of a sine wave is proportional to VP and frequency. With 20 percent less than the required slew rate, the output is distorted into a nearly triangle shape.

Large-signal square waves with very fast edges tilt on the rising and falling edges according to the slew rate of the amplifier. The final portion of a rising or falling edge will have rounding as the amplifier reaches its small-signal range, as shown in Figure 50.

In a noninverting circuit, a minimum 350-mV step is required to make this op amp slew, regardless of gain. **Figure 51** shows the slewing behavior for a 1-V input step with gains of 1, 2 and 4. The slew rate is the same for each gain (**Figure 52**). In G = 1, the output waveform

transitions to small-signal behavior in the final 350 mV. In G = 2 and G = 4, the small-signal portion is proportionally larger because the error signal fed back to the inverting input is attenuated by the feedback network. If connected in a gain greater than 50, this amplifier would be unlikely to slew because a 350-mV step would overdrive the output.

Slew rate is usually specified in voltage per microseconds, perhaps because early <u>general-purpose op amps</u> had slew rates in the range of 1 V/µs. Very <u>high-speed amplifiers</u> are in the 1,000-V/µs range, but you would rarely see it written as 1 kV/µs or 1 V/ns. Likewise, a <u>nanopower op amp</u> might be specified as 0.02 V/µs but seldom as 20 V/ms or 20 mV/µs. There's just no good reason why for some things; it is just the way we do it.

# 21. Settling time: a look at the character of the settling waveform

Settling time is the time required for an <u>operational amplifier</u> (op amp) to respond to an input-voltage step and then enter and stay within a specified error range of the final value. It is important in applications that drive an <u>analog-to-digital converter</u> (ADC), digitizing rapidly changing inputs. But let us look beyond the definition and focus on the character of settling waveforms.

Figure 53: As closed-loop gain is increased, bandwidth is reduced and response is slower.

In <u>section 20</u>, I showed how an op amp transitions from a slewing ramp to a small-signal settling portion of the waveform; see Figure 53. As the gain increases, you can see the slower closure to final value.

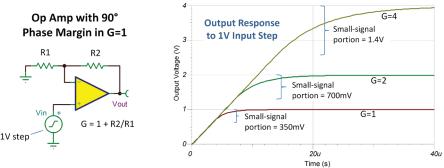

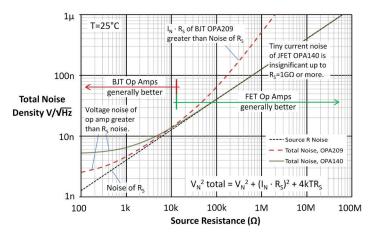

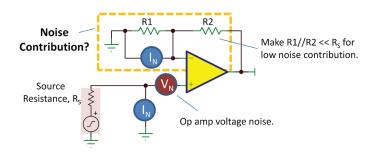

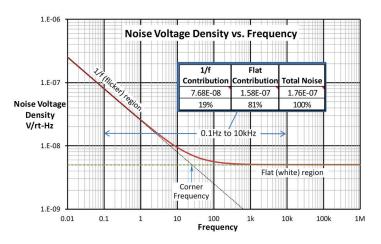

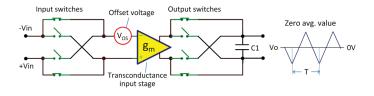

This is due to reduced closed-loop bandwidth in higher gain. This example op amp is tuned to have virtually 90 degrees phase margin in G = 1. Notice that there is no overshoot, even in unity gain. Its virtually perfect first-order response serves as a benchmark for comparison, but you are unlikely to find an op amp with such generous phase margin in G = 1.